Intel Unveils Industry’s First FPGA Integrated with High Bandwidth Memory

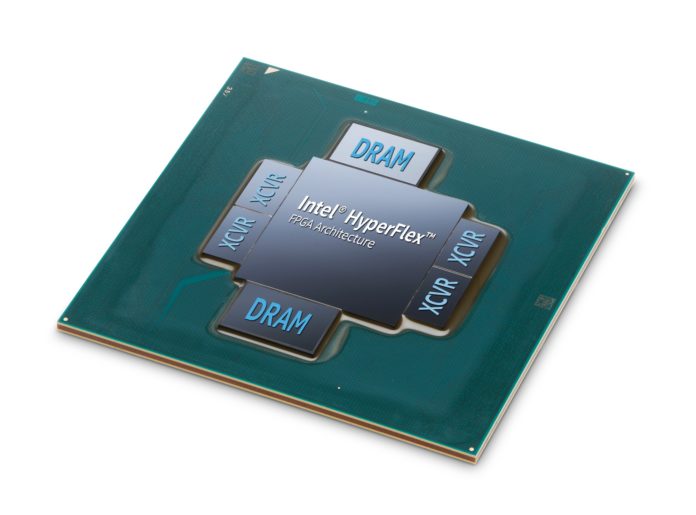

The Intel® Stratix® 10 MX FPGA is the industry’s first field programmable gate array (FPGA) with integrated High Bandwidth Memory DRAM (HBM2). By integrating the FPGA and the HBM2, Intel Stratix 10 MX FPGAs offer up to 10 times memory bandwidth compared to standalone DDR memory solutions. (Credit: Intel Corporation)

Intel just launched the Intel® Stratix® 10 MX FPGA, the industry’s first field programmable gate array (FPGA) with integrated High Bandwidth Memory DRAM (HBM2).

By coordinating the FPGA and the HBM2, Intel Stratix 10 MX FPGAs present to 10 times the memory data transfer capacity when contrasted and independent DDR memory solutions1. These transmission capacity abilities make Intel Stratix 10 MX FPGAs the fundamental multi-work quickening agents for superior registering (HPC), server farms, organize capacities virtualization (NFV), and communication applications that require equipment quickening agents to accelerate mass information developments and stream information pipeline systems.

Relies on HBM2, this industry’s first FPGA can pack and quicken bigger information developments contrasted and remain solitary FPGAs. With High-Performance Data Analytics (HPDA) situations, spilling information pipeline systems like Apache* Kafka and Apache* Spark Streaming require continuous equipment speeding up. Intel Stratix 10 MX FPGAs can all the while read/compose information and encode/unscramble information progressively without troubling the host CPU processor.

Reynette Au, vice president of marketing, Intel Programmable Solutions Group said, “To efficiently accelerate these workloads, memory bandwidth needs to keep pace with the explosion in data. We designed the Intel Stratix 10 MX family to provide a new class of FPGA-based multi-function data accelerators for HPC and HPDA markets.”

The Intel Stratix 10 MX FPGA family provides a maximum memory bandwidth of 512 gigabytes per second with the integrated HBM2. HBM2 vertically stacks DRAM layers using silicon via (TSV) technology. These DRAM layers sit on a base layer that connects to the FPGA using high-density micro bumps.

The Intel Stratix 10 MX FPGA family uses Intel’s Embedded Multi-Die Interconnect Bridge (EMIB) that rates correspondence between FPGA texture and the DRAM. EMIB attempts to proficiently incorporate HBM2 with a superior solid FPGA texture, settling the memory data transmission bottleneck in a power-effective way.

Related Post:

• Samsung Galaxy S8 and S8+ receiving fifth Android 8.0 Oreo beta, here's is what's changed.

• See Reasons Why Apple depends less on iPhone X.

• Apple Publishes Letter Of Apology To Their Customers About iPhone Batteries And Performance.

What is your opinion about this post? kindly let us know by your comment.

If you find this post helpful, consider to share this post to your friends and families

Like Our Facebook Page, Follow Us On Twitter, Subscribe To Our Youtube Channel's for more latest updates.

Thanks for this.. It really helped

ReplyDelete